着想力が豊かで,実行力が速く失敗を財産とできる前向きな志向の人材を育んでほしいナノサイエンスラボ 代表 門田 和也

高効率で即効性のある研究開発をやろう

聞き手:これから光学分野において活躍を目指す若手研究者・技術者,学生に向けて,門田さまの考える光の面白さ(魅力)など,メッセージをお願いします。門田:メッセージとしてお伝えしたいのは,「計算機予測を大いに活用し,高効率で即効性のある研究開発をやろう」です。その心は,「計算はコンピューターに任せ,脳みそは外のこと,次のことを考える」ことです。

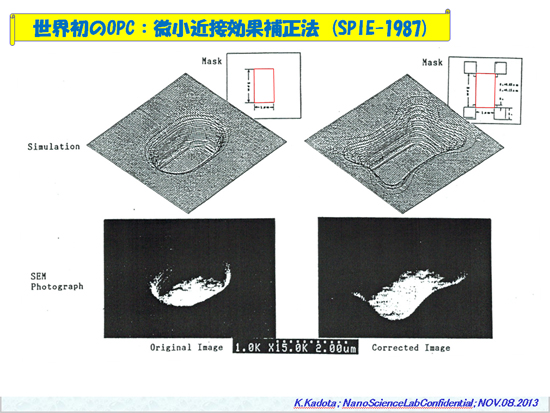

まず,1980年代後半,「近接効果補正(OPC)を大型計算機シミュレーションで行った」事例があります(図1)。

図1

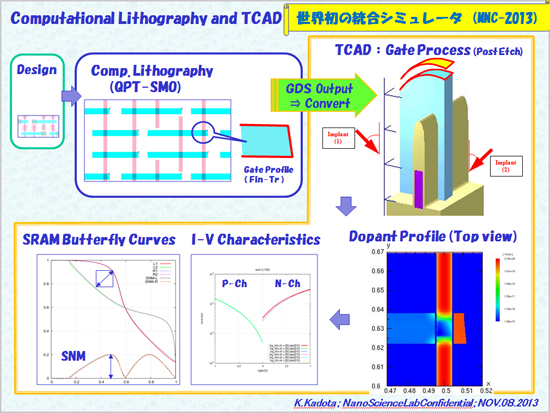

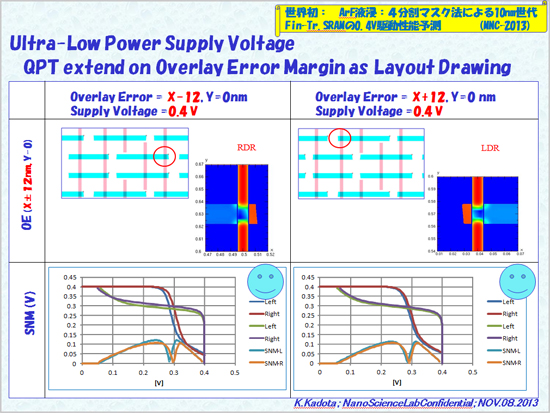

この手法は,レンズに光学収差等がある場合,それを補正する手段ともなります。また,マスク上にシステム欠陥が生じる場合,微小穴(OPC)を黒・白の欠陥に見立て,その影響を予測することも可能です。その後,2010 年代になり,「ArF液浸リソグラフィで4分割露光を実施した例」(図2)もあります。

図2

図3のVLSIテーラーのイラストは,87年にこれを発表したときに使ったスライドに入れたのですが,服を仕立てるのと同じように,LSIの設計を最適化するのにこういうパターンの出力を見て設計も直しましょう,というのを表現しています。今で言うと,「Design For Manufacturing」という考え方があります。それは後になってから作られた言葉ですが,当時から私は使っていました。

図3

図4

門田 和也(かどた・かずや)

1943年 神奈川県生まれ 1972年 東京工業大学 大学院理工学研究科 卒業 工学博士 1974年 日立製作所入社 2003年 定年退職後,産総研,東北大学を経て,ナノサイエンスラボ代表●研究分野

半導体設計

●主な活動・受賞歴等

半導体メモリ開発(特に微細加工技術を中心)

![研究室探訪vol.30 [奈良先端科学技術大学院大学 サイバネティクス・リアリティ工学研究室]](https://www.adcom-media.co.jp/wp-content/themes/adcom/scripts/timthumb.php?src=/wp-content/uploads/2022/11/laboratory1.jpg&w=80&h=100&zc=1&q=100)