OplusE 2012年8月号(第393号)

- 目次

- 特集のポイント

- 広告索引

特集

次世代高効率ネットワークデバイス技術

- ■総論

- 東京大学 浅見 徹

- ■大規模エッジルーターシステム化技術

- アラクサラネットワークス 渡辺 義則,馬場 淳志,山本 三夫,池田 尚哉

- ■大規模エッジルーターデバイス技術

- 日立製作所*,日本電気**,山梨日本電気***, 国際超電導産業技術研究センター****,富士通*****,篠田 和典*,山下 寛樹*,李 英根*,竹本 享史*,蔵田 和彦**,柳町 成行**,仁道 正明***,日高 睦夫****,鈴木 秀雄****,江川 満*****,西村 信治*

- ■超高速LAN-SANシステム化技術―40G OTN(WAN)向けキーデバイス技術―

- 技術研究組合光電子融合基盤技術研究所*,日本電信電話**,富士通***,三菱電機****,相澤 茂樹*,**,富澤 将人*,**,井出 聡*,***,大畠 伸夫*,****,有賀 博*,****

- ■超高速LAN-SANシステム化技術―スーパーハイビジョン配信―

- 産業技術総合研究所*,日本放送協会放送技術研究所**,黒須 隆行*,谷澤 健*,並木 周*,中戸川 剛**,小山田 公之**

- ■超高速LAN-SANデバイス技術

- 産業技術総合研究所*,富士通**,秋本良一*,石川 浩*,江川 満**,田中 有**

連載

- ■【一枚の写真】Bio-Texture Modeling®(生体質感造形®)」を用いた実物大臓器立体モデルによる手術支援

- 神戸大学 杉本 真樹

- ■【私の発言】撮る,見る,聞く。カメラは感性を表す道具

- ニコン 後藤 哲朗

- ■【第10・光の鉛筆】8 非点光線束の追跡1 現代の公式

- 鶴田 匡夫

- ■【波動光学の風景】第85回 87.透過型と反射型のホログラム

- 東芝 本宮 佳典

- ■【コンピュータイメージフロンティア VFX 映画時評】

- Dr.SPIDER

- ■【研究所シリーズ】海洋研究開発機構 高精度海底移動量計測を目指した海中レーザースティック

- 海洋工学センター 海洋技術開発部 探査機技術グループ 吉田 弘

- ■【ホビーハウス】形が定まらない物のコレクション

- 映像技術史研究家 鏡 惟史

コラム

■Event Calendar■掲示板

■O plus E News/「光学」予定目次

■New Products

■オフサイド

■次号予告

次世代高効率ネットワークデバイス技術東京大学大学院情報理工学系研究科 浅見 徹

1.はじめに

東日本大震災における原子力発電所の被災に伴い,昨年来節電が日本の国是としてうたわれている。ただし,省エネルギーへの問題意識は,少なくとも2000 年代半ばには,産業界全体でその重要性は認識されていた。特に,情報通信システムは,現状での総電力消費に占める割合は未だ小さいものの,技術イノベーションに伴う電力消費の増加速度は非常に速く,近い将来大きな割合になるとの危惧が出されていた。ブロードバンド先進国として有名な日本ではあるが,これからは,今までのFTTH(Fiber To The Home)に代表される高速化以外に省エネルギー化の道をも模索しなければならない状況にある。一方,今日の情報通信の物理層を担う基幹技術として考えた場合,光通信ネットワークは,省エネルギー性という観点からも非常に優れた技術である。そこで,本特集号においては,ネットワークの高効率化を支える光デバイス技術に関して,新エネルギー・産業技術総合開発機構(NEDO)の次世代高効率ネットワークデバイス技術開発プロジェクト(2007~2011 年)1)の研究成果を基に紹介する。2.プロジェクトの目標と進め方

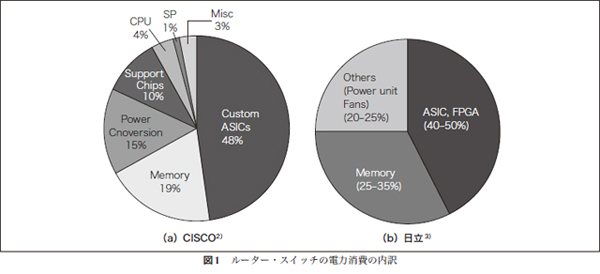

省エネルギー化という観点では,このプロジェクトは,経済産業省の研究開発プログラム(PG)である「ITイノベーションPG」(情報ネットワークシステムの徹底的省エネの実現)と「エネルギーイノベーションPG」(省エネ型情報生活空間創生技術)に基づいており,先行プロジェクトであるフェムト秒テクノロジー(1995~2004 年)やフォトニックネットワーク技術開発(2002~2006 年)において確立した光デバイス技術(光源・受光器・スイッチなど)をベースに,高速かつ低消費電力のデバイス技術を開発することを目的として進められた。最初から,研究の産業界への出口を指向して進めた点が,先行プロジェクトとの大きな相違点である。図1に米CISCO Systems 社2)と(株)日立製作所3)によるルーター・スイッチの電力消費に関した発表データを示した。CISCOのデータでは,Custom ASICs(48%)とMemory(19%)だけで全体のほぼ70%を消費しているが,ASIC, FPGA, Memoryが3/4を占める日立のデータも同傾向であり,これを裏付けている。現代ルーター・スイッチは,ルーティングに,TCAM(Ternary CAM;三値連想メモリー)と高速Memoryを使うのが特徴である。セキュリティー対策の高まりに合わせTCAMはパケットフィルター等にも多用される傾向にあり,上記70%のかなりの割合は,TCAM 関連デバイスで消費されていると考えられる。一方,本プロジェクトでは,光インターフェース回路の省エネルギー化を検討したが,その消費エネルギーは,図1のASICやSupport Chipsの一部を占めるに過ぎない。しかし,回線速度の高速化に伴ってこの部分の省電力の増加速度は大きく,絶対値としては無視できない消費電力となっていくと考えた。

また,2006 年時点で,ネットワークのEthernetへの集約,および100GbE/40GbE 標準化の進行が顕在化していたことを踏まえ,100Gbit/sのEthernet(100GbE)でのルーター接続を前提に適用可能なデバイス技術の開発と,実用化に向けた検証をターゲットにした。この結果,光デバイスの研究開発だけではなく,その周辺回路,特に超高速回路のCMOS(Complementary Metal OxideSemiconductor)実装による低消費電力化も大きな課題となった。

一方,広域ネットワーク(WAN:Wide Area Network)では,多波長は運用コストが高いこと,100Gbit/sシングル波長にはまだ技術的課題が多いことから,4 波長25Gbit/sから成る100GbE 標準以外に,SDH(SynchronousDigital Hierarchy)で運用経験を積んだ40Gbit/sシングル波長伝送を踏まえたEthernet 標準技術も,WANとの親和性を考えると必要であると認識し,その標準化と技術開発を並行して実施した。先行する10Gbit/s×4のEthernet 規格があったため,この新規の40Gbit/sシングル波長Ethernet(以下40GbEと称す)市場を形成するには,IEEE(Institute of Electrical and Electronic Engineers)で40GbEの標準化をしなければならず,その活動と,WAN規格であるOTU(Optical Channel Transport Unit)3eの標準化をITU-T(International TelecommunicationUnion Telecommunication Standardization sector)で運動した点も大きな特徴である。

このような観点から,本プロジェクトでは25Gbit/sと40Gbit/s 関連の光/電気伝送技術の小型省電力化に注力した。プロジェクト運営に関しては,開発技術のシステム的位置づけを明確にするため,デバイスやモジュールの開発をシステム開発と並行して進め,お互いにフィードバックできるよう心がけた。このため,25Gbit/s 光/電気伝送技術に関して「大規模エッジルーターシステム化技術」および,40Gbit/s 光/電気伝送技術に関して「超高速光LAN-SAN(Local Area Network-Storage AreaNetwork)システム化技術」という2つのプロジェクトを基盤に推進した。以下では,それぞれについて成果の概要を示す。

3.25Gbit/s 光/電気伝送技術:100GbEと光バックプレーン

大規模エッジルーターシステム化技術のプロジェクトを中心に進められた25Gbit/s 光/ 電気伝送技術は,100GBASE-LR4,スケーラブル・ルーターアーキテクチャおよび光バックプレーン,SFQ(Single FluxQuantum;単一磁束量子)ベース・リアルタイム波形モニター,温度安定・高速直接変調レーザーが主なサブテーマである。3.1. 100GBASE-LR4

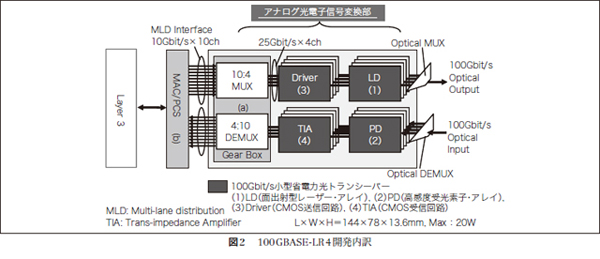

プロジェクトで目指した100GbE 標準技術である100GBASE-LR4における開発部分を図2に示した。図の(1)~(4)で示した部分が本プロジェクトで開発した100Gbit/s 小型省電力光トランシーバーであり,プロジェクト期間中に100GBASE-LR4の基本部分すべてをプロトタイプとして実現することに成功した。 図2のLD(Laser Diode)としては25Gbit/s×4チャンネルの面出射型レーザーアレイを開発し,85℃で15mA(1.3μm)と低しきい値,かつ光出力角8°以下を非球面レンズ集積技術で実現した。また,65nm CMOSプロセスによりTIA(Trans-impedance Amplifier;電流電圧変換増幅器)アレイを開発し,3.0mW/Gbit/s,トータルで295mWの低電力動作を実現した。PD(Photodiode)は,最大35GHzの高速動作と0.8A/W(1.3μm)以上の高い受光感度を持つ4チャンネルアレイで実現した。±10μmの位置ずれを許容できることが特徴である。PD(高感度受光素子・アレイ),TIA(CMOS 受信回路),LD(面出射型レーザー・アレイ),Driver(CMOS 送信回路)を合わせて4チャンネルの入出力を持つCMOSハイブリッド集積を実現した。消費電力は20mW/Gbit/sと低消費電力である。

図2のLD(Laser Diode)としては25Gbit/s×4チャンネルの面出射型レーザーアレイを開発し,85℃で15mA(1.3μm)と低しきい値,かつ光出力角8°以下を非球面レンズ集積技術で実現した。また,65nm CMOSプロセスによりTIA(Trans-impedance Amplifier;電流電圧変換増幅器)アレイを開発し,3.0mW/Gbit/s,トータルで295mWの低電力動作を実現した。PD(Photodiode)は,最大35GHzの高速動作と0.8A/W(1.3μm)以上の高い受光感度を持つ4チャンネルアレイで実現した。±10μmの位置ずれを許容できることが特徴である。PD(高感度受光素子・アレイ),TIA(CMOS 受信回路),LD(面出射型レーザー・アレイ),Driver(CMOS 送信回路)を合わせて4チャンネルの入出力を持つCMOSハイブリッド集積を実現した。消費電力は20mW/Gbit/sと低消費電力である。

3.2. 光バックプレーン

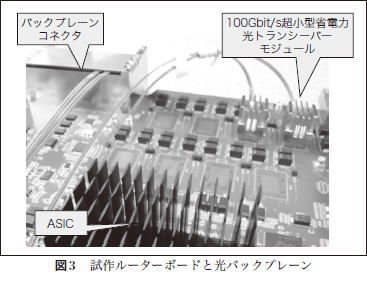

光バックプレーンに関しては,近年通信距離と速度の面で限界に達しているルーター・スイッチのバックプレーンを1.3μm 波長の光伝送路で置換することにより,距離の制限を緩和された,超高速(100Gbit/s),省電力(10mW/Gbit/s)な光バックプレーンで置き換えることを実現した。 図3のバックプレーンコネクタの右隣の100Gbit/s 超小型光トランシーバーは,100GbEの開発で用いたトランシーバーである。実際にルーターとして実装した結果,空調の観点からも有用な技術であることが判明した。

図3のバックプレーンコネクタの右隣の100Gbit/s 超小型光トランシーバーは,100GbEの開発で用いたトランシーバーである。実際にルーターとして実装した結果,空調の観点からも有用な技術であることが判明した。

3.3. スケーラブル・ルーターアーキテクチャとSFQベース・リアルタイム波形モニター

開発技術の直接の応用先としては,ネットワークの運用をも想定した。ネットワークの運用技術の面では,スケーラブル・ルーターアーキテクチャとリアルタイム波形モニターを重視した。スケーラブル・ルーターアーキテクチャは,高速光ネットワークに対応可能なトラフィックモニタリング技術(40Gbit/sおよび4Mフロー/sに対応する独立筐きょうたい体型およびルーター内蔵トラフィック分析技術および装置)を開発することを中間目標に定めた。最終目標は,さらに進めてそれらを実現する光バックプレーンの開発とした。 まず,トラフィックモニタリングに関しては,モニター対象トラフィックに含まれるフロー数と比べて非常に少ない統計情報格納用メモリーで動作するAFM(Aggregated Flow Mining)技術と呼ぶ特徴フロー抽出アルゴリズムをハードウエア化し,10Gbit/s 対応トラフィック分析装置として開発した。これを4 台組み合わせて40Gbit/s,4Mフロー/sのトラフィックモニターを実現し,既存の1Gbit/sを大幅に高速化した40Gbit/sのWANに対応したモニター技術を確立できた。光バックプレーンは,複数のトラフィック分析装置を相互接続するための要素技術である。

まず,トラフィックモニタリングに関しては,モニター対象トラフィックに含まれるフロー数と比べて非常に少ない統計情報格納用メモリーで動作するAFM(Aggregated Flow Mining)技術と呼ぶ特徴フロー抽出アルゴリズムをハードウエア化し,10Gbit/s 対応トラフィック分析装置として開発した。これを4 台組み合わせて40Gbit/s,4Mフロー/sのトラフィックモニターを実現し,既存の1Gbit/sを大幅に高速化した40Gbit/sのWANに対応したモニター技術を確立できた。光バックプレーンは,複数のトラフィック分析装置を相互接続するための要素技術である。SFQベース・リアルタイム波形モニターに関しては,100GbEの基本信号である25Gbit/s 光信号のリアルタイム波形観測を目指して保守運用に供すことを目標に開発し,50GS/s,5bitの超電導ADコンバーターを実現した。副次的成果として,交流標準電圧発生装置(パルス駆動型ジョセフソン交流電圧標準発生装置)に応用可能と分かっている。

3.4. 温度安定・高速直接変調レーザー

100GbEのレーザー部分は,温度変化の激しい個所に組み込む必要があるため,温度安定性に優れている必要がある。このため,温度安定・高速直接変調レーザーとして,高密度量子ドット8 層積層構造を活性層に用いた量子ドットレーザーの研究開発を次世代LDとして位置づけて実施した。1.3μm 波長用であり,面密度5.9×1010cm-2,室温正味モード利得55cm-1(世界最高),25Gbit/sの直接変調(量子ドットレーザーで世界初)を実現した。40Gbit/s 光/電気伝送技術:40GbEと172Gbit/sOTDM

一方,40Gbit/s 光/電気伝送技術に関しては,超高速LAN-SANシステム化技術を,「超高速LAN-SANシステム化技術―40G OTN*1)(WAN)向けキーデバイス技術―」と「超高速LAN-SANシステム化技術―スーパーハイビジョン(SHV)配信―」にプロジェクトを分けて推進した。4.1 超高速LAN-SANシステム化技術―40G OTN(WAN)向けキーデバイス技術―

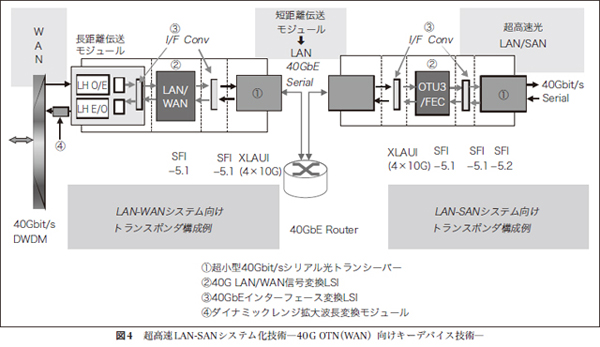

このシステム化プロジェクトでは,近未来のサービスを考えると40GbE 接続が重要であり,10Gbit/s×4の40GbE 規格に加え,40Gbit/s×1の伝送が可能な40GbEシリアル伝送規格をIEEEに提案し,標準化とシステム実装を行った。図4は「超高速LAN-SANシステム化技術―40G OTN(WAN)向けキーデバイス技術―」の構成図である。WANでの40GbE 利用に関しては,OTU3eをITU-T 標準として決め,商用化を目指して信号処理回路のLSI(Large Scale Integration)化に尽力した。 図4の①超小型40Gbit/sシリアル光トランシーバー,②40G LAN-WAN 信号変換LSI,③40GbEインターフェース変換LSI,④ダイナミックレンジ拡大光増幅器(SOA:Semiconductor Optical Amplifier)によるマッハツェンダー干渉計(MZI)型波長変換器,低消費電力・超高速直接変調レーザーが関連デバイス技術である。

図4の①超小型40Gbit/sシリアル光トランシーバー,②40G LAN-WAN 信号変換LSI,③40GbEインターフェース変換LSI,④ダイナミックレンジ拡大光増幅器(SOA:Semiconductor Optical Amplifier)によるマッハツェンダー干渉計(MZI)型波長変換器,低消費電力・超高速直接変調レーザーが関連デバイス技術である。

4.1.1. 超小型40Gbit/sシリアル光トランシーバー

図4の①に示した超小型40Gbit/sシリアル光トランシーバーは,大きさ91.5×41.8mm,消費電力5.6Wという従来比でサイズが1/3 以下,電力1/2 以下のトランシーバーであり,40GbEシリアル,40G VSR(VeryShort Reach)向けに開発した。特に,40GbEシリアル光トランシーバーとしては世界に先駆けて実現し,同標準化に貢献している。キーテクノロジーはSFI-5.2(VSR)またはXLAUI(40GbE MLD)信号を39.8/41.2/43Gbit/sシリアル信号へ変換する40Gbit/s CMOS 多重・分離LSIと超小型送信モジュールである。4.1.2. 40G LAN/WAN 信号変換LSI

40G LAN/WAN 信号変換LSI(図4の②)は,LANインターフェース[SFI-5.1(STM256 /OC768)またはSFI-4(STM64/OC192, 10GbE)]をWANインターフェース[SFI-5.1(OTU3/OTU3e)]へ変換する消費電力5.6W以下のLSIである。4.1.3. 40GbEインターフェース変換LSI

40GbEインターフェース変換LSI(図4の③)は,SFI-5.1(OTU3/OTU3e)をSFI-5.2/XLAUIに変換するLSIであり,16:4が示すように,SFI-5.1は2.4G×16,SFI-5.2は10G×4で後者の方がはるかにコンパクトになっている。消費電力は4W 以下である。4.1.4. ダイナミックレンジ拡大SOA-MZI 型波長変換器

ダイナミックレンジ拡大SOA-MZI 型波長変換器は,ファイバー長の長短に起因する入力信号光パワーの10dB(+3dBm ~ +13dBm)の変動にも耐え得る波長変換器である。SOAによるMZIを用い,入力ダイナミックレンジの拡大のためにフィードバック制御を行っているところに特徴があり,720μm×4800μmの大きさに収まっている。4.1.5. 高速直接変調レーザー

超小型40Gbit/sシリアル光トランシーバーのさらなる低消費電力化と小型化を目指すため,低消費電力・超高速直接変調レーザー(図5の43G LD 次世代版)として,短い活性層(100μm 以下)の前後にブラッグ反射鏡(DBR:Distributed Bragg Reflector)を集積した高抵抗埋め込み,AlGaInAs(アルミニウム・ガリウム・インジウム・ヒ素)系の低消費電力・超高速直接変調レーザーを開発した。 40GbEのLDの将来技術としての位置づけであり,1.5μm 波長では駆動電流44mAで85℃,40Gbit/s 動作を確認し,1.3μm 波長では70℃までの40Gbit/s 光ファイバー伝送を達成し,後者は世界初である。消費電力も従来比1/2で40Gbit/s 直接変調を実現している。

40GbEのLDの将来技術としての位置づけであり,1.5μm 波長では駆動電流44mAで85℃,40Gbit/s 動作を確認し,1.3μm 波長では70℃までの40Gbit/s 光ファイバー伝送を達成し,後者は世界初である。消費電力も従来比1/2で40Gbit/s 直接変調を実現している。

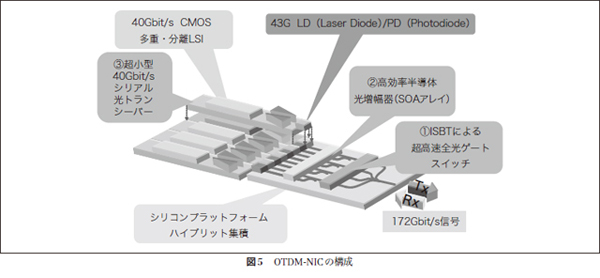

4.2. 超高速LAN-SANシステム化技術―SHV 配信―

「超高速LAN-SANシステム化技術―SHV 配信―」に関しては,SHVのサービスイン後を想定し,スタジオ内でコンテンツを作成する環境を踏まえて技術開発を行った。要求仕様は,映像コンテンツの圧縮伸長に伴う画像劣化を避けるためには,非圧縮伝送が必須であることで,その結果,72~144Gbit/s 伝送の実現がシステム目標となった。作成システムでは,64 本のHD-SDI 信号(High Definition Serial Digital Interface;ハイビジョンの規格信号,1.5Gbit/s) を8 本ごとにまとめて10Gbit/s 信号に変換し,それを4 本まとめて40Gbit/sのOTU(Optical Channel Transport Unit)3 信号に変換する構成とした。これを172Gbit/s 信号へ多重化する役割を担うのが,サブバンド間遷移(ISBT:InterSubBandTransition) を用いたOTDM(Optical Time DivisionMultiplex)による4チャンネル多重化であり,市販光スイッチと組み合わせてLANを構成できる。開発項目は,図5の① ISBTによる超高速全光ゲートスイッチと②高効率半導体光増幅器である。ISBTによる集積全光ゲートスイッチは,インジウムガリウムヒ素/アルミニウムヒ素アンチモン(InGaAs/AlAsSb)量子井戸導波路ISBTを利用した全光位相変調技術をベースにしており,数psという高速応答時間と1.0rad/pJ*2)という高い効率を実現した。このゲートスイッチをコア技術にOTDM-NIC(Network InterfaceCard)を構成し,40Gbit/s×4のMUX/DEMUX*3)ができることを立証した。ここで,多重単位にはこだわらないこと,対象となるSHVの速度が高々144Gbit/sであったことから,40Gbit/s×4の多重化とし,図5の③に4.1.1の超小型40Gbit/sシリアル光トランシーバーを流用することによって開発コストを下げている。OTDMの技術的ポイントは,40Gbit/sの電子回路技術があれば光波長多重により電子回路の制約なく640Gbit/s 以上まで高速化が図れることであり,データセンター内でのサーバー間の超高速接続などにも利用が期待できる。また,OTDMは従来クロックの重畳が難しかったが,産業技術総合研究所の自主技術であるインバンド・クロック送信機構を使えば,光スイッチの切り替え後数十msもあれば特殊な付加回路なしで迅速に伝送が再開できることが確認できた。

一方,高効率半導体光増幅器は,1.5μm 帯を想定し,コラムナ量子ドット多層化による高効率半導体光増幅器であり,50℃,40Gbit/sの高温動作の実現と4チャンネルアレイ化を実現している。

5.超精密加工計測技術

以上が,NEDOの支援を受け,昨年度で完了した次世代高効率ネットワーク技術開発プロジェクトの成果である。以下に,「大規模エッジルーターシステム化技術」およびそのデバイス技術,「超高速LAN-SANシステム化技術―40G OTN(WAN)向けキーデバイス技術―」,「超高速LAN-SANシステム化技術―SHV 配信―」,およびそのデバイス技術に分けて詳説することにしたい。光デバイスとEthernetのつながりに興味がある読者のお役にたてれば幸いである。参考文献

- 荒川泰彦:“ 次世代高効率ネットワーク技術開発プロジェクトと研究諸課題~デバイス基盤技術の概要~”, 信学技報, Vol. 107,No. 250, pp. 7~11 (2007)

- G. Epps, D. Tsiang, and T. Boures : “System PowerChallenges,” Cisco Routing Research Seminar, August 29-30(2006)

- M. Yamada, T. Yazaki, S. Nishimura, and N. Ikeda :“Technologies to save power for carrier class routers andswitches,” Proc. of the International Symposium onApplications and the Internet table of contents,pp.385~388(2008)

![研究室探訪vol.30 [奈良先端科学技術大学院大学 サイバネティクス・リアリティ工学研究室]](https://www.adcom-media.co.jp/wp-content/themes/adcom/scripts/timthumb.php?src=/wp-content/uploads/2022/11/laboratory1.jpg&w=80&h=100&zc=1&q=100)